Category:AND gate symbols

Jump to navigation

Jump to search

Media in category "AND gate symbols"

The following 70 files are in this category, out of 70 total.

-

20030729123656!Und-Gatter.png 53 × 85; 348 bytes

-

2И.jpg 80 × 76; 14 KB

-

3-Input AND ANSI.svg 100 × 50; 5 KB

-

3-Und-Gatter-Schaltsymbol DIN40700.png 85 × 108; 422 bytes

-

3AND.png 121 × 80; 805 bytes

-

3И.jpg 80 × 76; 15 KB

-

AND ANSI Labelled.svg 120 × 50; 7 KB

-

AND ANSI.svg 100 × 50; 389 bytes

-

AND BS.svg 100 × 60; 5 KB

-

AND DIN.svg 100 × 80; 5 KB

-

AND from NAND and NOT.svg 200 × 50; 13 KB

-

AND from NAND.svg 200 × 50; 14 KB

-

AND Gate diagram.svg 721 × 232; 3 KB

-

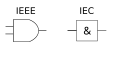

AND gate IEC and IEEE.svg 1,521 × 744; 9 KB

-

AND gate RU.svg 170 × 100; 826 bytes

-

AND gate with three inputs.svg 108 × 34; 1 KB

-

AND Gate.svg 176 × 67; 3 KB

-

AND gate.svg 120 × 74; 100 KB

-

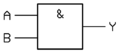

AND IEC Labelled.svg 120 × 50; 7 KB

-

AND IEC.svg 100 × 50; 5 KB

-

And kapısı.png 87 × 162; 6 KB

-

AND poort.jpg 304 × 129; 10 KB

-

AND using NAND.svg 217 × 40; 10 KB

-

AND-gate-IEC.png 134 × 79; 1 KB

-

AND-gate-US.png 134 × 79; 1 KB

-

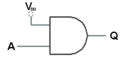

And-gate.png 305 × 124; 3 KB

-

AND-Gate.png 160 × 116; 2 KB

-

AND-grind.PNG 160 × 84; 821 bytes

-

AND-grind.svg 512 × 269; 1 KB

-

AND-poort symbolen.png 151 × 179; 1 KB

-

And.png 128 × 48; 713 bytes

-

And.svg 500 × 180; 4 KB

-

AND2N-gate-US.svg 413 × 205; 5 KB

-

AOI21Symbol.svg 65 × 32; 4 KB

-

AOI22Symbol.svg 65 × 42; 5 KB

-

Bramka log AND.svg 256 × 141; 2 KB

-

BUF from AND with Bounded law.png 358 × 204; 4 KB

-

CPT-logic-gate conversion NAND-NOT.svg 175 × 69; 39 KB

-

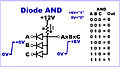

Diode AND2 Ideal Diode.jpg 4,341 × 2,408; 783 KB

-

Et-nand.png 191 × 47; 1 KB

-

Fonctions logiques(3-e).png 162 × 70; 1 KB

-

FTA AND gate.jpg 86 × 151; 2 KB

-

Funcion logica Y.PNG 482 × 142; 3 KB

-

Hradlo-and.png 250 × 150; 2 KB

-

IEC AND De Morgan label.svg 170 × 75; 5 KB

-

IEC AND label.svg 170 × 75; 3 KB

-

IEC AND.gif 128 × 74; 600 bytes

-

IEC AND.svg 128 × 74; 530 bytes

-

Ir elementas.png 99 × 65; 715 bytes

-

ISN-porte-et.svg 430 × 174; 4 KB

-

Logic circuit AND 00 jp.svg 250 × 100; 19 KB

-

Logic circuit AND 01 jp.svg 250 × 100; 18 KB

-

Logic circuit AND 10 jp.svg 250 × 100; 18 KB

-

Logic circuit AND 11 jp.svg 250 × 100; 17 KB

-

Logic circuit AND jp.svg 250 × 100; 14 KB

-

Logic-gate-and-de.png 640 × 282; 1 KB

-

Logic-gate-and-de.svg 640 × 282; 5 KB

-

Logic-gate-and-iec.png 640 × 282; 780 bytes

-

Logic-gate-and-us.png 640 × 282; 1 KB

-

Logic-gate-and-us.svg 500 × 180; 4 KB

-

Logical and.svg 200 × 75; 5 KB

-

LogicAndGate3Inputs.svg 141 × 111; 3 KB

-

MFrey AND with 3 Inputs 002.svg 160 × 80; 7 KB

-

Puerta AND.svg 300 × 100; 5 KB

-

Puerta lógica 002.svg 150 × 75; 5 KB

-

SimboloAND.png 132 × 61; 1 KB

-

Und-Gatter.png 188 × 85; 629 bytes

-

Verilog Simple Assignment.svg 125 × 70; 10 KB

-

Veya.png 75 × 153; 7 KB

-

و.png 128 × 48; 556 bytes