File:Metastability D-Flipflops.svg

From Wikimedia Commons, the free media repository

Jump to navigation

Jump to search

Size of this PNG preview of this SVG file: 730 × 560 pixels. Other resolutions: 313 × 240 pixels | 626 × 480 pixels | 1,001 × 768 pixels | 1,280 × 982 pixels | 2,560 × 1,964 pixels.

Original file (SVG file, nominally 730 × 560 pixels, file size: 28 KB)

File information

Structured data

Captions

Captions

Add a one-line explanation of what this file represents

Summary

[edit]| DescriptionMetastability D-Flipflops.svg |

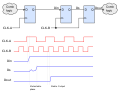

English: Metastability in digital circuits: Simplified schematic how a data line can cross different (asynchronous) clock domains (CLK_A and CLK_B) to minimize the risk of metastability with a double buffer D-Flipflop chain.

Русский: Схема возникновения метастабильного состояния в триггере тактируемом по фронту сигнала |

| Date | |

| Source | Own work |

| Author | wdwd |

| Other versions |

|

Licensing

[edit]I, the copyright holder of this work, hereby publish it under the following license:

This file is licensed under the Creative Commons Attribution-Share Alike 4.0 International license.

- You are free:

- to share – to copy, distribute and transmit the work

- to remix – to adapt the work

- Under the following conditions:

- attribution – You must give appropriate credit, provide a link to the license, and indicate if changes were made. You may do so in any reasonable manner, but not in any way that suggests the licensor endorses you or your use.

- share alike – If you remix, transform, or build upon the material, you must distribute your contributions under the same or compatible license as the original.

File history

Click on a date/time to view the file as it appeared at that time.

| Date/Time | Thumbnail | Dimensions | User | Comment | |

|---|---|---|---|---|---|

| current | 17:56, 1 October 2017 |  | 730 × 560 (28 KB) | GliderMaven (talk | contribs) | Fixed logic/timing error on diagram waveform |

| 18:46, 21 January 2017 |  | 730 × 560 (28 KB) | GliderMaven (talk | contribs) | minor change to the waveform to make it more characteristic of metastability | |

| 18:04, 5 December 2015 |  | 730 × 560 (27 KB) | Wdwd (talk | contribs) | add arrows | |

| 18:03, 5 December 2015 |  | 730 × 560 (27 KB) | Wdwd (talk | contribs) | add arrows | |

| 20:44, 25 November 2015 |  | 730 × 560 (27 KB) | Wdwd (talk | contribs) | == {{int:filedesc}} == {{Information |Description={{en|Metastability in digital circuits: Simplified schematic how a data line can cross different (asynchronous) clock domains (CLK_A and CLK_B) to minimize the risk of metastability with a double buffer... |

You cannot overwrite this file.

File usage on Commons

The following 3 pages use this file:

File usage on other wikis

The following other wikis use this file:

- Usage on de.wikipedia.org

- Usage on en.wikipedia.org

- Usage on he.wikipedia.org

- Usage on uk.wikipedia.org

Metadata

This file contains additional information such as Exif metadata which may have been added by the digital camera, scanner, or software program used to create or digitize it. If the file has been modified from its original state, some details such as the timestamp may not fully reflect those of the original file. The timestamp is only as accurate as the clock in the camera, and it may be completely wrong.

| Width | 730 |

|---|---|

| Height | 560 |

Hidden categories: